수업 내용 정리-2

CPU: (=Central Processor, 마이크로프로세서, 중앙 처리 장치) - 사람의 뇌와 같은 역할을 한다. 데이터를 연산한다.

cpu는 명령어, 데이터 인출(Fetch), 명령어 해독(Decode), 데이터 처리(execute), 데이터 기록(write back)을 한다.

- 인출: 명령어의 주소를계산하고, 그 주소로 가서 명령어를 가져온다. 만약, 명령어 실행을 위해 데이터가 필요한 경우 기억장치 혹은 입력장치로부터 데이터를 읽어온다.

- 해독: 수행해야할 동작을 결정하기 위해 인출된 명령어를 해독한다.

- 처리: 데이터에 산술연산 혹은 논리연산을 수행한다.

- 기록: 수행한 결과를 저장한다.

cpu는 연산장치(ALU), 레지스터, 제어장치로 구성된다.

ALU: 산술연산, 논리연산을 담당한다.

ALU는 데이터 레지스터, 보수기, 가산기, 누산기, 오버플로우 검출기, 상태 레지스터로 구성된다.

- 데이터 레지스터: 연산에 사용할 데이터를 일시적으로 기억한다.

- 보수기: 뺄셈을 덧셈으로 처리하기 위해 빼는 수를 보수로 바꿔준다.

- 가산기: 두 데이터를 받아서 덧셈 연산을 한다.

- 누산기(AC): 연산한 결과를 일시적으로 보관(저장)한다.

- 오버플로우 검출기: 산술 연산의 결과값이 레지스터 용량보다 커서 저장할 수 없을 때, 오류를 발생시킨다.

- 상태 레지스터: 연산 중 자리올림, 오버플로우, 양수, 음수, 0 등의 결과값의 상태를 나타낸다.

레지스터: 명령을 순서대로 저장하는 장치, cpu가 동자하기 위해 필요한 데이터나 명령 등을 임시로 저장하는 공간.

- 명령어 계수기(PC): 다음에 실행하게 될 명령어의 주기억 장치 내 주소를 기억한다.

- 주소 레지스터(MAR): 주기억 장치에 명령이나 데이터가 기억되어 있는 주소를 보관한다.

- 버퍼 레지스터(MBR): 명령어 계수기가 지정하는 주기억 장치의 내용을 임시로 보관한다.

- 명령어 레지스터(IR): 현재 수행 중인 명령 코드를 보존하는 레지스터(명령어 코드/주소 필드)

제어장치: 실제로 명령을 해석해 처리하는 장치이다. 제어 신호 발생기와 주소 처리기로 나뉜다.

주기억 장치에 있는 명령어를 차례대로 해독하고 제어 신호를 발생하면 각 장치들이 동작한다.

[제어 신호 발생기]

- 제어 신호 발생기: 명령어 레지스터(IR)의 명령 코드 해독, 명령어 수행을 위한 제어 신호 발생

- 순서기: 주소 처리기를 동작시킨다.

[주소 처리기]

- 수행될 명령어의 주소를 계산한다.

- 이를 명령어 계수기(PC)에 저장한다.

<CPU 작동 순서>

- 명령어 주소 전송: 명령어 계수기(PC) --주소--> 메모리 주소 레지스터(MAR)

- 명령어 전송: 주기억 장치 --명령어--> 명령어 레지스터(IR)

- 명령어 코드 필드 -> 해독기, 주소 필드 -> 주소 처리기

- 주소 처리기에서 처리-연산: 연산 해줘야 할 데이터의 주소 계산

-> 다음 명령어 호출 : 다음 명령어 주소 계산 => 명령어 계수기(PC)에 저장 - 제어 신호 발생기에서 처리-해독기: 연산자 해독, 명령어 수행을 위한 제어 신호 발생

-순서기: 주소 처리기를 동작시켜 수행될 명령어 주소 계산 => 수행 순서 변경 - 이 과정을 반복한다.(IR에 있는 명령어 수행이 끝나면 PC값을 MAR에 보내서 다음 명령어 실행)

cpu 안에 alu와 제어를 하는 제어(cu) unit이 있고,레지스터가 있다.

레지스터는 특수한 목적을 기족 설계된 저장공간이다. 연산과정에서 연산에 필요한 값들을 저장하고 결과를 반환한다.

연산을 한 후에 지연시간이 있으면 성능이 떨어지므로 방지를 위해 메모리 계층 구조를 사용한다.

(+ memory unit(메모리 관리 장치)은 cpu가 메모리에 접근하는 것을 관리하는 장치(부품)이다.)

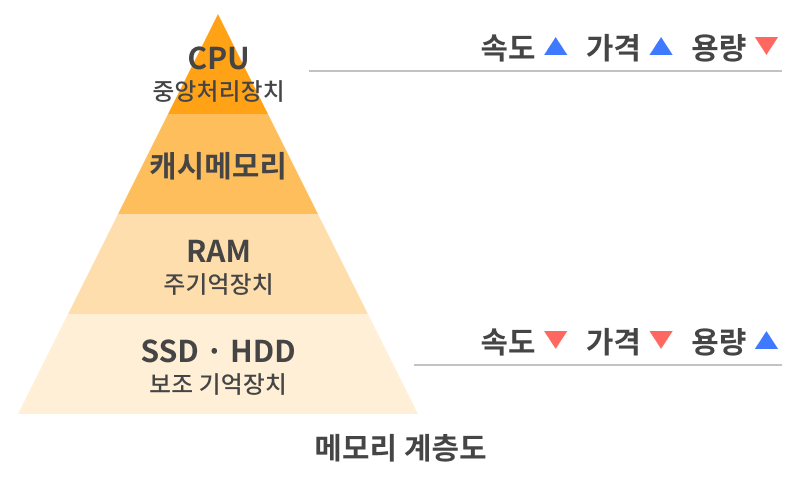

[메모리 계층 구조]

- register

- cache

- ram

- ssd, hdd

밑으로 내려갈 수록 용량이 올라가고 느려지고 싸진다.

hdd에서 ram으로 ram에서 cache로, cache에서 레지스터에 잠깐 저장했다가 연산을 한다.

레지스터와 캐시는 cpu안에 있고 작고 빠르고 비싸다.

따라서 큰 시스템을 만들려면 적절하게 배치해서 용량과 속도를 모두 챙겨야한다.

각각의 특징을 갖는 메모리들을 함께 사용해서, 최적의 효율을 낼 수 있다. 상황에 맞게 사용해서

가격의 이점과 높은 성능을 동시에 챙기는 컴퓨터를 설계할 수 있다.

레지스터는 바이트 단위 용량이고, 속도는 1나노초보다 작다. 용량이 작고 엄청 빠르다.

ISA

명령어 집합 구조이다.

소프트웨어가 하드웨어에 명령를 내리는데 이에 대한 인터페이스를 정의한 것들(집합)을 말한다.

cpu마다 명령 체계(ISA)가 다르다.

소프트웨어가 내리는 명령어에 해당되는 기계어를 정하여 모은 ISA로는 x86/x64, ARM 등이 있다.

ISA는 cpu에서 명령어가 실제로 기계어로 어떻게 동작하는지를 모아놓은 집합이고,

이에 대한 부분집합으로 CPU를 설계하는 방식의 종류들이 있는데, 대표적으로 CISC와 RISC이다.

즉, ISA를 구현(만들기) 위해 cpu를 설계하는 방식들인 것이다.

CISC는 고급언어에 맞춰서 기계어를 일대일로 대응시킨 회로를 많이 설계하는, cpu 설계 방식이다.

명령어를 많이 설계하게 되면 해석해야 될 것이 많아지고, 이로 인해서 cpu의 구조가 복잡해진다.

대신 필요한 명령어가 많이 존재하므로 컴파일러와 코드는 간단해진다.

x86/64는 cisc 방식으로 설계된 cpu에서 동작하는 ISA이다.

RISC는 고급 명령어에 맞는 기계어를 일대일로 대응시킨 회로를 적게 설계하는, cpu 설계 방식이다.

명령어를 조금 설계하고 필요한 명령어는 조합해서 사용한다. 따라서 cpu의 구조는 간단해진다.

cpu는 간단해지지만, 대신 이로 인해서 컴파일러와 코드가 복잡해진다.

ARM이 risc 방식으로 설계된 cpu에서 동작하는 ISA이다.

(MIPS는 임베디드나 네트워크를 설계할 때 사용된다.)